**PIN STRUCTURE OF PORT 1,2,3**

## **Port-1 Pin Structure:**

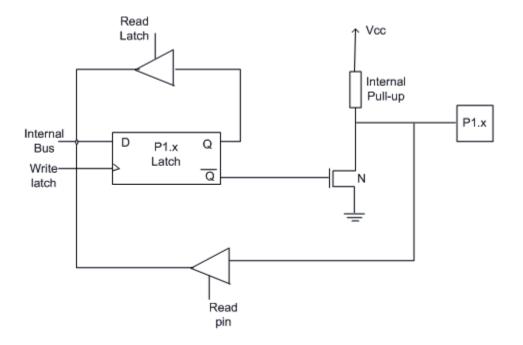

Port-1 has 8 pins (P1.1-P1.7) . The structure of a port-1 pin is shown in fig 15

## Fig 15. Port 1 Structure

Port-1 does not have any alternate function i.e. it is dedicated solely for I/O interfacing. When used as output port, the pin is pulled up or down through internal pull-up. To use port-1 as input port, '1' has to be written to the latch. In this input mode when '1' is written to the pin by the external device then it reads fine. But when '0' is written to the pin by the external device then the external source must sink current due to internal pull-up. If the external device is not able to sink the current the pin voltage may rise, leading to a possible wrong reading.

## **Port-2 Pin Structure:**

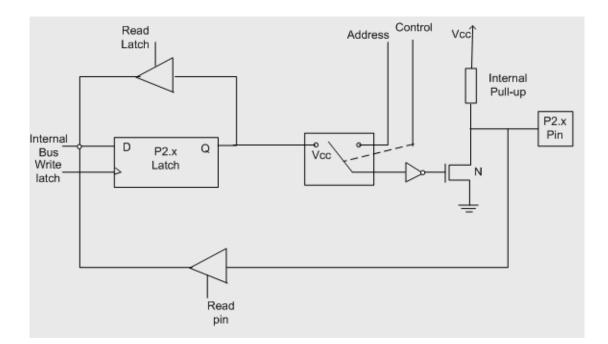

Port-2 has 8-pins (P2.0-P2.7). The structure of a port-2 pin is shown in fig 14.

Fig. 16.PORT 2 Pin Structure

Port-2 is used for higher external address byte or a normal input/output port. The I/O operation is similar to Port-1. Port-2 latch remains stable when Port-2 pin are used for external memory access. Here again due to internal pull-up there is limited current driving capability.

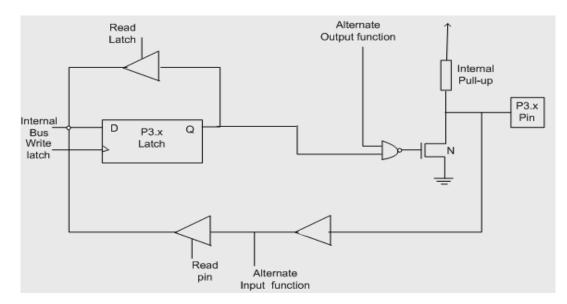

## **Port-3 Pin Structure:**

Fig. 17.PORT 3 Pin Structure:

Each pin of Port-3 can be individually programmed for I/O operation or for alternate function. The alternate function can be activated only if the corresponding latch has been written to '1'. To use the port as input port, '1' should be written to the latch. This port also has internal pull-up and limited current driving capability.

Alternate functions of Port-3 pins -

| P3.0 | RxD  |

|------|------|

| P3.1 | TxD  |

| P3.2 | INTO |

| P3.3 |      |

| P3.4 | T0   |

| P3.5 | T1   |

| P3.6 | WR   |

| P3.7 | RD   |

Note:

- 1. Port 1, 2, 3 each can drive 4 LS TTL inputs.

- 2. Port-0 can drive 8 LS TTL inputs in address /data mode. For digital output port, it needs external pull-up resistors.

- 3. Ports-1,2and 3 pins can also be driven by open-collector or open-drain outputs.

Each Port 3 bit can be configured either as a normal I/O or as a special function bit. Reading a port (portpins) versus reading a latch. There is a subtle difference between reading a latch and reading the output port pin.

The status of the output port pin is sometimes dependant on the connected load. For instance if a port is configured as an output port and a '1' is written to the latch, the output pin should also show '1'. If the output is used to drive the base of a transistor, the transistor turns 'on'. If the port pin is read, the value will be '0' which is corresponding to the base-emitter voltage of the transistor. *Reading a latch:* Usually the instructions that read the latch, read a value, possibly change it, and then rewrite it to the latch. These are called "read-modify-write" instructions. Examples of a few instructions are-

ORL P2, A; P2 <-- P2 or A

MOV P2.1, C; Move carry bit to PX.Y bit

In this the latch value of P2 is read, is modified such that P2.1 is the same as Carry and is then written back to P2 latch.

Reading a Pin: Examples of a few instructions that read port pin, are-

MOV A, P0; Move port-0 pin values to A

MOV A, P1; Move port-1 pin values to A

Source : http://elearningatria.files.wordpress.com/2013/10/ece-iv-microcontrollers-10es42-notes.pdf