## DAC AND BINARY-WEIGHTED RESISTOR DAC

A DAC converts an abstract finite-precision number (usually a fixed-point binary number) into a concrete physical quantity (e.g., a voltage or a pressure). In particular, DACs are often used to convert finite-precision time series data to a continually-varying physical signal.

A typical DAC converts the abstract numbers into a concrete sequence of impulses that are then processed by a reconstruction filter using some form of interpolation to fill in data between the impulses. Other DAC methods (e.g., methods based on Delta-sigma modulation) produce a pulse-density modulated signal that can then be filtered in a similar way to produce a smoothly-varying signal.

By the Nyquist–Shannon sampling theorem, sampled data can be reconstructed perfectly provided that its bandwidth meets certain requirements (e.g., a baseband signal with bandwidth less than the Nyquist frequency). However, even with an ideal reconstruction filter, digital sampling introduces quantization that makes perfect reconstruction practically impossible. Increasing the digital resolution (i.e., increasing the number of bits used in each sample) or introducing sampling dither can reduce this error.

DACs are at the beginning of the analog signal chain, which makes them very important to system performance. The most important characteristics of these devices are:

Resolution: This is the number of possible output levels the DAC is designed to reproduce. This is usually stated as the number of bits it uses, which is the base two logarithm of the number of levels. For instance a 1 bit DAC is designed to reproduce 2 (21) levels while an 8 bit DAC is designed for 256 (28) levels. Resolution is related to the effective number of bits(ENOB) which is a measurement of the actual resolution attained by the DAC.

Maximum sampling frequency: This is a measurement of the maximum speed at which the DACs circuitry can operate and still produce the correct output. As stated in the Nyquist–Shannon sampling theorem, a signal must be sampled at over twice the frequency of the desired signal. For instance, to reproduce signals in all the audible spectrum, which includes frequencies of up to 20 kHz, it is necessary to use DACs that operate at over 40 kHz. The CD standard samples audio at 44.1 kHz, thus DACs of this frequency are often used. A common frequency in cheap computer sound cards is 48 kHz—many work at only this frequency, offering the use of other sample rates only through (often poor) internal resampling.

Monotonicity: This refers to the ability of a DAC's analog output to move only in the direction that the digital input moves (i.e., if the input increases, the output doesn't dip before asserting the correct output.) This characteristic is very important for DACs used as a low frequency signal source or as a digitally programmable trim element.

THD+N: This is a measurement of the distortion and noise introduced to the signal by the DAC. It is expressed as a percentage of the total power of unwanted harmonic distortion and noise that accompany the desired signal. This is a very important DAC characteristic for dynamic and small signal DAC applications.

Dynamic range: This is a measurement of the difference between the largest and smallest signals the DAC can reproduce expressed in decibels. This is usually related to DAC resolution and noise floor.

Other measurements, such as phase distortion and sampling period instability, can also be very important for some applications.

## **BINARY-WEIGHTED RESISTOR DAC**

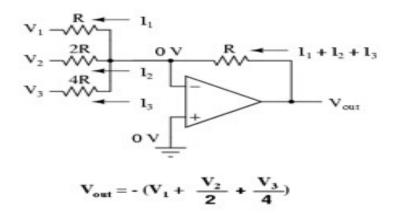

The binary-weighted-resistor DAC employs the characteristics of the inverting summer Op Amp circuit. In this type of DAC, the output voltage is the inverted sum of all the input voltages. If the input resistor values are set to multiples of two: 1R, 2R and 4R, the output voltage would be equal to the sum of V1, V2/2 and V3/4. V1 corresponds to the most significant bit (MSB) while V3 corresponds to the least significant bit (LSB).

The circuit for a 4-bit DAC using binary weighted resistor network is shown below:

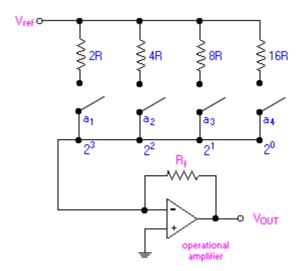

The binary inputs, ai (where i = 1, 2, 3 and 4) have values of either 0 or 1. The value, 0, represents an open switch while 1 represents a closed switch.

The operational amplifier is used as a summing amplifier, which gives a weighted sum of the binary input based on the voltage, Vref.

For a 4-bit DAC, the relationship between Vout and the binary input is as follows:

$$\begin{split} V_{\text{our}} &= - \, \mathrm{i} \mathbb{R}_{f} \\ &= - \left[ V_{\text{ref}} \left( \frac{a_{1}}{2\mathbb{R}} + \frac{a_{2}}{4\mathbb{R}} + \frac{a_{3}}{8\mathbb{R}} + \frac{a_{4}}{16\mathbb{R}} \right) \right] \mathbb{R}_{f} \\ &= - \, \frac{V_{\text{ref}} \, \mathbb{R}_{f}}{\mathbb{R}} \left( \frac{a_{1}}{2} + \frac{a_{2}}{4} + \frac{a_{3}}{8} + \frac{a_{4}}{16} \right) \\ &= - \, \frac{V_{\text{ref}} \, \mathbb{R}_{f}}{\mathbb{R}} \left( \frac{a_{1}}{2^{1}} + \frac{a_{2}}{2^{2}} + \frac{a_{3}}{2^{3}} + \frac{a_{4}}{2^{4}} \right) \end{split}$$

The negative sign associated with the analog output is due to the connection to a summing amplifier, which is a polarity-inverting amplifier. When a signal is applied to the latter type of amplifier, the polarity of the signal is reversed (i.e. a + input becomes -, or vice versa).

For a n-bit DAC, the relationship between Vout and the binary input is as follows:

$$V_{\text{OUT}} = -\frac{V_{\text{ref}} R_{f}}{R} \sum_{i=1}^{n} \frac{a_{i}}{2^{i}}$$

Analog Voltage Output: An Example

As an example, consider the following given parameters: Vref = 5 V, R = 0.5 k and Rf = 1 k. The voltage outputs, Vout, corresponding to the respective binary inputs are as follows:

| Dig        | gital | Inp | ut | VOUT (Volts)  |

|------------|-------|-----|----|---------------|

| <b>a</b> 1 | a2    | a3  | a4 | v 001 (v 0h3) |

| 0          | 0     | 0   | 0  | 0             |

| 0          | 0     | 0   | 1  | - 0.625       |

| 0          | 0     | 1   | 0  | - 1.250       |

| 0          | 0     | 1   | 1  | - 1.875       |

| 0          | 1     | 0   | 0  | - 2.500       |

| 0 | 1 | 0 | 1 | - 3.125 |

|---|---|---|---|---------|

| 0 | 1 | 1 | 0 | - 3.750 |

| 0 | 1 | 1 | 1 | - 4.375 |

| 1 | 0 | 0 | 0 | - 5.000 |

| 1 | 0 | 0 | 1 | - 5.625 |

| 1 | 0 | 1 | 0 | - 6.250 |

| 1 | 0 | 1 | 1 | - 6.875 |

| 1 | 1 | 0 | 0 | - 7.500 |

| 1 | 1 | 0 | 1 | - 8.125 |

| 1 | 1 | 1 | 0 | - 8.750 |

| 1 | 1 | 1 | 1 | - 9.375 |

Table 1: Voltage Output of 4-bit DAC using Binary Weighted Resistor Network

The LSB, which is also the incremental step, has a value of - 0.625 V while the MSB or the full scale has a value of - 9.375 V.

Practical Limitations:

The most significant problem is the large difference in resistor values required between the LSB and MSB, especially in the case of high resolution DACs (i.e. those that has large number of bits). For example, in the case of a 12-bit DAC, if the MSB is 1 k then the LSB is a staggering 2 M

The maintanence of accurate resistances over a large range of values is problematic. With the current IC fabrication technology, it is difficult to manufacture resistors over a wide resistance range that maintain an accurate ratio especially with variations in temperature.

Source : https://aihteienotes.files.wordpress.com/2014/07/lic-notes.doc